In FET I-vs-V with Analog Discovery 2, I plotted Id vs. Vgs curves for an nFET:

The Ids-vs-Vgs curves do not superimpose as nicely as curves I’ve measured with PteroDAQ. I don’t yet understand why not.

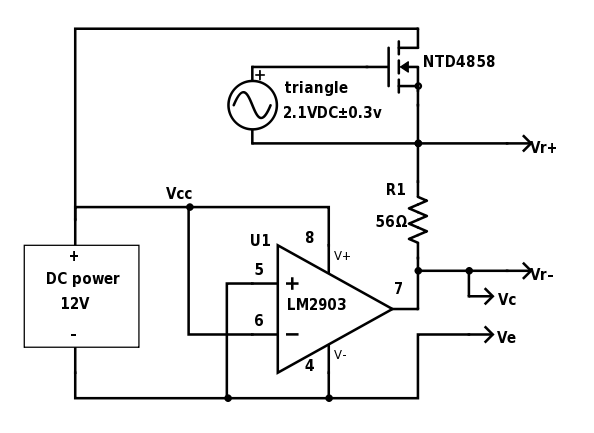

Yesterday, I played with sweeping the power supply (Power waveform generator). In this post, I used that capability to plot Id vs Vds curves for different gate voltages (Vgs) of a different nFET (since the AOI518 is an obsolete part). The setup is the same as for the previous test—the function generator is connected to the gate, the power supply to the drain load resistor in series with the nFET whose source is connected to ground, and the two oscilloscope channels monitor the voltage across the load resistor and across the nFET. The difference is that I use the power-waveform option to put a 1Hz triangle wave on the power supply, but put just a DC offset (AC amplitude 0V) on the function generator output, so that the gate voltage is constant as the drain voltage is adjusted.

The saturation regions are well plotted up to Vgs=2.7V. I averaged 10 or 20 scans for each of these curves, to reduce quantization noise for small voltages or small currents.

I got quite different results when I removed and replaced the nFET from the breadboard—the breadboard contacts seem to have a variation of about ±0.05Ω in resistance, which is much larger than the on-resistance of the nFET when fully on. I took measurements with a wire between the source and drain to estimate the wiring resistance, but wiggling the wire produced very different results.

In the next graph, I tried subtracting off the wiring resistance to get the on-resistance, but I’m really quite dubious about the measurements smaller than 0.5Ω, because of the unrepeatability of the bread board contact resistance.

The numbers here look good (close to the spec sheet), but repeating the measurements could result in ±0.1Ω, which makes the Ron measurements for fully on transistors rather useless.

By using a smaller power resistor, I could probably get saturation currents for slightly higher gate voltages, up to the current limit of the power supplies in the Analog Discovery 2, but better on-resistance measurements would require a better jig for making low-resistance contacts to the FET.

By using a much larger resistor, I could measure low currents more accurately, which would give me a better idea of the leakage currents—I don’t really believe the measurements for Vgs=2.1V, because the current appears to decrease with increasing Vds, which is probably an artifact of measuring a small difference in voltage with a large common-mode signal.

I tried using larger resistors to measure the saturation currents, but the results varied a lot depending on what size load resistor is used. I believe that the difference is due to temperature changes from self-heating. If I sweep out to larger Vds voltages (using a smaller load resistor, hence smaller IR drop across it), but about the same saturation current, I’m dissipating more power in the transistor, so making it warmer. This appears to increase the saturation current. Reducing the range of the voltage with the same load resistor drops the curve down, just as increasing the load resistor does. I suspect that proper measurement requires a jig that holds the transistor at a nearly constant temperature, as well has having very low contact resistance.

The saturation current seems to vary by about ±10% as I change load resistors. The effect is most likely thermal—note that using a smaller voltage sweep for Vgs=2.3V and Rload=51Ω resulted in almost the same curve as Rload=270Ω, because the power dissipated was about the same.

Note that the thermal explanation also works for explaining why the superposition does not work well for the Id vs Vgs plots—at lower load resistances, more power is dissipated in the transistor, and it gets warmer, shifting the current curve upward.