2017 December 31

Twenty-sixth weight progress report

This post is yet another weight progress report, continuing the previous one, part of a long series since I started in January 2015.

Although I managed to get my weight back within my target range around the end of October, I’ve not managed to keep it there.

Long term, random fluctuations are about ±3 pounds, but there is an upward drift of about 3 pounds a year that I need to resist.

My goal is to lose five pounds and keep them off—staying in the middle of my target range, but this may be harder to achieve than I had originally envisioned three years ago when I started on the weight-control effort.

November and December had me riding an average of only 3.29 miles a day—over the whole year about 3.6 miles a day. In a week, my exercise will go back up, as I’ll be cycling to campus five times a week, for winter and spring quarters. That guarantees me 4.6 miles a day average, which will get me off to a good start. But summer and next fall’s sabbatical will probably reduce the exercise hours again.

My family did get in a nice walk yesterday (about 5.6 miles with 580 feet of climb).We had mapped out 3 possible routes before we went for the walk, with different turnaround points depending on how tired we felt. We ended up taking the middle of the three.

We started from home, walked to the end of Escalona, along the bike path to Harvey West Park, then took the Harvey West trail and Pogonip Creek trail to the Pogonip, up through the Pogonip to the Spring Trail, then back down the Spring Trail, Spring Street, and Laurent Street to home. It’s been years since I’ve walked in the Pogonip, and I’ve never walked the Harvey West and Pogonip Creek trails before. They were very quiet and shady—we saw a lot more walkers on the Spring Trail and on the trails near Golf Club Drive.

The shorter route would not have reached the meadows of the Pogonip, turning up Lookout Trail up to Spring Street (cutting off about 1.4 miles). The longer route would have taken us up to the Spring Box/Koi Pond and then come down Coolidge Drive rather than Spring Trail, adding about 1.6 miles. (Google maps has all the major trails in the Pogonip marked, if you want to see where we went.)

Somewhat surprisingly, my wife, who does the most walking of any of us on a daily basis, was the slowest of the group. My son and I walked at abut the same pace, with his youth compensating for his lack of routine exercise.

2017 December 24

Choosing a grad school

One of my more popular posts has been Where you get your BS in CS matters, which looked at a report on which universities sent students on to PhD programs in computer science. Choosing a college for undergraduate studies based on reputation or rankings is always problematic, because the ratings generally measure the wrong thing (usually size, wealth, and reputation, rather than educational quality).

Choosing a grad school is also difficult. Reputation for research quality matters more for choosing a grad school than for an undergraduate, because grad students are expected to do research and their future careers may be highly affected by the reputation of their advisers or grad schools. But overall reputation is not enough—reputation within a subfield is what matters most.

An important question for students applying to grad schools to ask is whether the places they are applying to (or are accepted at) will provide a rich environment for the sort of research they want to do.

When I was applying to grad schools (44 years ago), I made the mistake of looking only at overall reputation, and chose the math department at Stanford. The first year in math grad programs consisted of three subjects: real analysis, complex analysis, and abstract algebra (I believe that math grad program have not changed this focus in the past 4 decades). After I passed my comprehensive exams (3 grueling 6-hour exams), I started looking for a thesis topic and an adviser and realized that no one in Stanford’s math department at the time did the sort of math I enjoyed (discrete math: combinatorics and graph theory). Luckily, Stanford’s computer science department had four faculty in those fields, and the CS department there accepted my application for a transfer. As it turned out, I didn’t end up doing combinatorics, graph theory, or any of the mathematical computer science subfields—I flirted with a lot of subjects (including computer music) and my thesis was in computer-aided design for VLSI.

Grad school applicants nowadays don’t have to make my mistake—they have access to much more information and much finer-grained information about grad programs than was easily available 40 years ago. One resource worth looking at is CS Rankings, which ranks computer science programs based on publications in some of the top conferences in computer science. In addition to the raw rankings (which can be highly misleading), the website also provides pie charts that give the breakdown of the publications by field.

For example, UC Berkeley is ranked top of the UC system and the pie chart shows particular strength in robotics, vision, and machine learning. UC Santa Barbara is ranked as number 26, with particular strengths in security, databases, and electronic design automation (EDA).

But the particular method used is problematic, because of the reliance on a small number of conferences. For example, UCSC’s strength in bioinformatics is not visible, because most of the publications are in biology journals (and glam journals like Nature), not in the two conferences that the rankings use (RECOMB and ISMB). Conference publications are the main coin of the realm in most of CS, but not in bioinformatics, where journal publications rule. UCSC’s strength in storage systems is also not well represented, because FAST and USENIX ATC (two of the major conferences in that field) are not included.

The CSRankings.org method has some weird artifacts (like rewarding short author lists that exclude students and postdocs) and can be gamed in various ways. Indeed, the ranking of institutions has changed enormously in the last two weeks, as departments have scrambled to up their averages by including affiliated faculty with high weighted publication counts and exclude those with low ones.

Despite the rather serious limitations of the CSrankings.org method, it is a more informative and useful system for comparing grad schools than ones like US News and World Report’s, which seem to bear almost no relationship with reality, being based almost entirely on hearsay reputation.

The best thing to use the CSRankings for is to look for what fields an institution is strong in (keeping in mind that many fields are not properly represented by the selection of conferences) and what faculty are publishing highly in the conferences that the CSRankings organizers think are important. Grad school applicants should follow up by looking at the web pages of the faculty in the subfields that interest them (and check to make sure that the faculty are still there—people move around and a strong subfield 5 years ago may be missing now as faculty moved to industry or other academic positions).

2017 December 22

Breakout board for SOT-23 FETs

After a discussion in the comments of Ron vs Vgs for pFETs and nFETS with Michael Johnson, I decided to design my own breakout boards for SOT-23 surface-mount FETs, with the possible use of them in the class-D amplifier lab in place of the through-hole TO-220 FETs we’ve been using.

I picked a couple of 30V FETs (one nFET, one pFET) whose data sheets indicated that they would have adequately low on-resistance with a gate voltage of only 2.5V (–2.5V for the pFET), so that the FETs could be controlled by a 3.3V logic signal with no problems. I ended up picking PMV20XNER for nFET (14.9¢ in 100s) and SSM3J332R for pFET (12.4¢ in 100s).

Although the drain-to-source voltage is allowed to go to 30V, the gate-to-source voltage is more limited (±12V for both the nFET and the pFET). That should be adequate for anything we do in the course, as our maximum power supply is ±5V, so we shouldn’t see any voltage differences bigger than 10V. (I could have saved a few cents by using 20V FETs instead of 30V ones, maybe.)

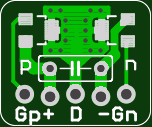

Because the students use the FETs in an H-bridge, I decided to make my breakout board be a half H-bridge, with an nFET, a pFET, a bypass capacitor, and 5 right-angle header pins:

The layout took me a while, because I wanted to make as much heat sinking as I could get on a small, cheap board. The standard footprint for a ST-23 allows a thermal resistance of about 120 K/W. I did not push too hard though, because even with ideal layout, the SOT-23 packages still have terrible thermal conductivity (about 90 K/W)—essentially all the heat is being conducted through the thin drain pin. (The SSM3J332R reports even worse numbers: 300 K/W with minimum footprint and 120 K/W with a square inch of copper.)

Solder side of the board. Visualization provided by https://gerber-viewer.easyeda.com/

Component side of the board. Visualization provided by https://gerber-viewer.easyeda.com/

My board is not nearly a square inch of copper—the entire board is only 15mm × 12.5mm, and only half of that is used for heatsinking the drains. I used the back of the board for radiating heat and provided thermal vias around the drain pads to connect the front and back. The footprint for the pads is one provided by the manufacturers for wave soldering—I thought it would be easier for had soldering than the much smaller pads used for reflow soldering.

The gate connections are on the outside, the source connections just inboard of them, and the shared drain in the middle. The board is basically symmetric with respect to nFET and pFET, but I labeled the two sides so that there would be less variation in how students soldered them up.

The bypass capacitor is close to the FETs (much closer than the students ever got on a bread board), so we should see less noise injection back into the power rails than we’ve seen in the past. The resistance of the source and drain traces adds another 5mΩ of resistance to the H-bridge, which is not too bad—the beardboard probably adds more like 50mΩ.

If I understood their website correctly, I should be able to get 10 copies of the tiny board panelized in a 6×7 array (so 420 boards after I cut them apart) for only $4.90 from Smart-Prototyping.com. Of course, I’m in a hurry, so I ended up paying an extra $23.79 for shipping with DHL, so the order costs $28.69, or <7¢ a board. I also ordered 10 40-pin right-angle male headers (enough for 80 boards) for $4.11 from AliExpress, raising the price to 12¢ a board.

With the transistors, each half H-bridge will cost under 40¢ in 100s—much less than the approximately $1.37/half H-bridge that the separate TO-220 FETs cost.

The difference in cost is not important for the course ($2 a student), so my main consideration is whether the students will learn more by doing some surface mount soldering with a fixed cMOS half-H-bridge design or by continuing to wire up separate transistors on the bread board (making the usual student errors of getting the pinout wrong or general miswiring). There is still plenty of room for error on the half H-bridge: swapping transistors, getting 2 nFET or 2 pFET instead of one of each, putting the whole board in backwards to short the power supply through the body diodes, …. .

The SOT-23s can’t dissipate quite as much heat as the TO-220s, but we’ll probably not have much heat to dissipate in reasonable designs. With a 5V supply, 8Ω load, and 73mΩ on-resistance, the power dissipation in the pFET should be only about 28mW and the nFET even less—way less than the 500mW or so that I expect the boards to be able to handle. Shoot-through current is mainly what the students will need to worry about, as that can get quite high with the low on-resistances of both the nFET and the pFET.

I’ve ordered the boards and parts to test out using the SOT-23 FETs and half-H-bridge boards. If they work out well, I’ll probably rewrite the class-D lab to have students do a little surface-mount soldering (SOT-23s are about the simplest intro).

2017 December 20

Ron vs Vgs for pFETs and nFETS

My son has joked that I don’t have an electronics hobby—I have a hobby of characterizing transistors. There is an uncomfortable amount of truth in that assertion—I spend more time measuring things with my tools than building things.

Today I wanted to characterize all the nFETs and pFETs that I have, so that I could choose the right ones for the class-D amplifier lab in spring quarter—also to see whether the on resistances were as low at the data sheet claimed.

I used just the Analog Discovery 2, some 10W resistors (to make the 24Ω load), and a Schottky diode as a fly-back diode (because the power resistors have a fairly large inductance). I chose the load so that the power supplies on the Analog Discovery 2 would not exceed their 2.1W limit. In the past I’ve used a wall wart with a higher current limit to do power FET tests, but I figured that the 400mA test current was enough for what I wanted to do today.

I swept the gate voltage with a 1-second ramp, turning the transistor on abruptly but off slowly. I determined the gate voltage just from the timing, as I used the two oscilloscope channels to measure the drain-to-source voltage Vds and the drain current Id.

The results of measuring the pFETs. Only the low-threshold IPP45P03P4L11AKSA1 turns on at –3.3V. The funny knees in the curve around 10Ω are where the test jig switches from being roughly constant current (~400mA) to having a current dependent on Ron (Vds is no longer nearly 0).

To get the on resistance, I fit the data from –10V to –9V with a straight line and used that straight line at Vgs=–10V to get the value.

IPP45P03P4L11AKSA1 is no longer available, but NTD2955-1G and IRFU9024NPBF still are—it’s too bad that they aren’t really turned on at —3.3V. Perhaps I should get myself some IRLIB9343PBF pFETS and test them—they supposedly have a very low threshold and reasonably low Ron. They cost a bit more, but they do have the longer leads that allow breadboarding. I looked at the data sheet for the IRLIB9343PBF, and it does not look very promising—the resistance shoots up at about –5V. The SPP15P10PLHXKSA1 looks more promising on the datasheet.

I have a lot more nFETs than pFETs, so I tested all of them also. The circuit is essentially the same as for the pFETs, just swapping the voltage sources and turning the fly-back diode around. I also changed the direction of the ramp, so that I was still turning on the FET abruptly and off slowly.

One of the outliers, IPU50R950CEAKMA1, is a high-voltage nFET. It has both a high threshold and a high Ron, but it can handle much larger voltages than the others—it was intended for switching rectified mains voltages (about 350V), but I’ve not used it yet. The other two outlier nFETs (2N7000TA and TN2106N3-G) are not power FETs—I had to switch to a 48Ω load to measure them, to avoid putting too much current through them.

The AOI514 and AOI518 parts are obsolete. The NTD4858N-35G is still available, but it has very short leads, and we had problems last year with them popping out of the breadboards. The NTD5867 is now only available as a surface-mount part, but the PSMN022-30PL,127 is still available and has long leads that work in the breadboard.